-

About

-

Business

- Business TOP

- Semiconductor/Electronic devices

- FA System/Control equipment

- Power electronics/Renewable energy

- Semiconductor manufacturing equipment/Measuring instruments

- Pneumatic hydraulic equipment/conduction equipment

- Electronic materials/Chemical materials

- Defense products/Telecommunications Infrastructure

- Broadcasting-related

- ICT / DX / EC

-

Service

-

Network

-

Supplier

- Career

- Contact

About UsAbout

View More

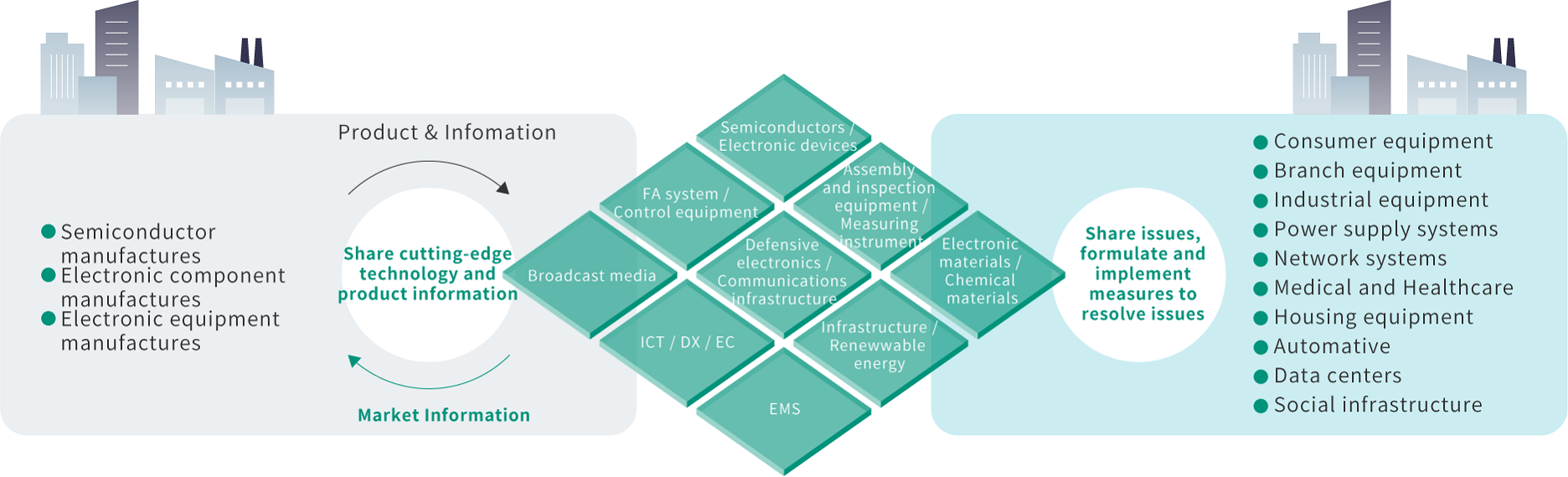

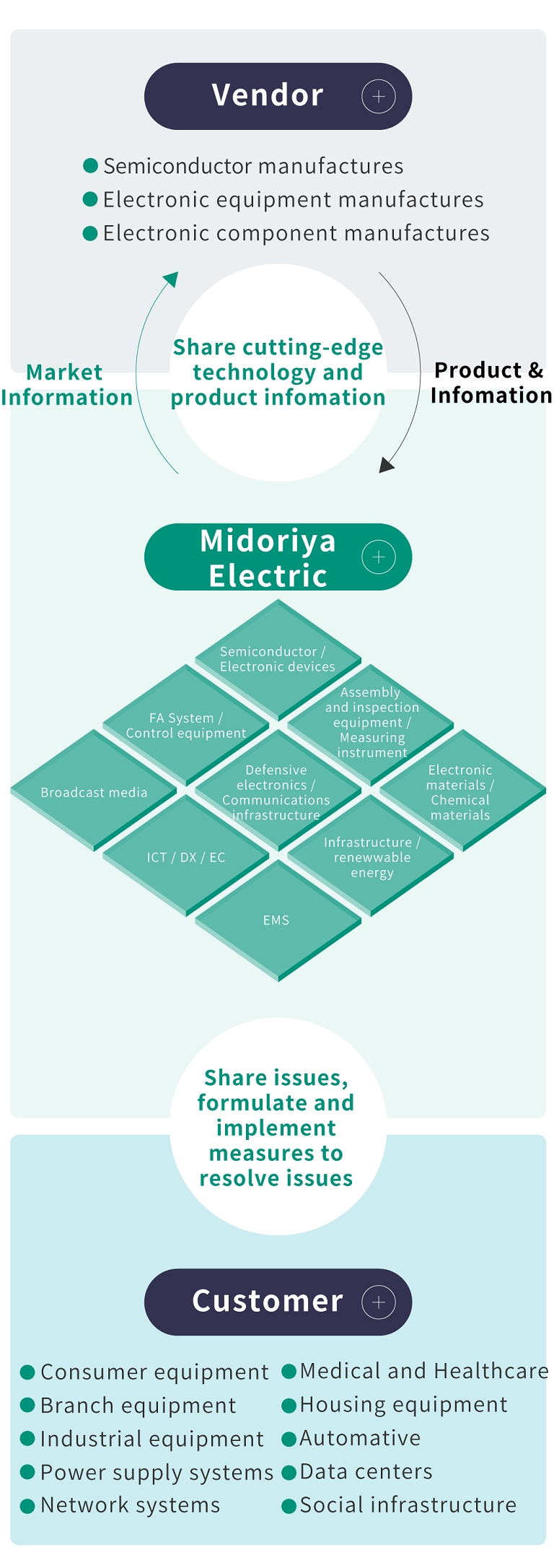

BusinessBusiness

View More

-

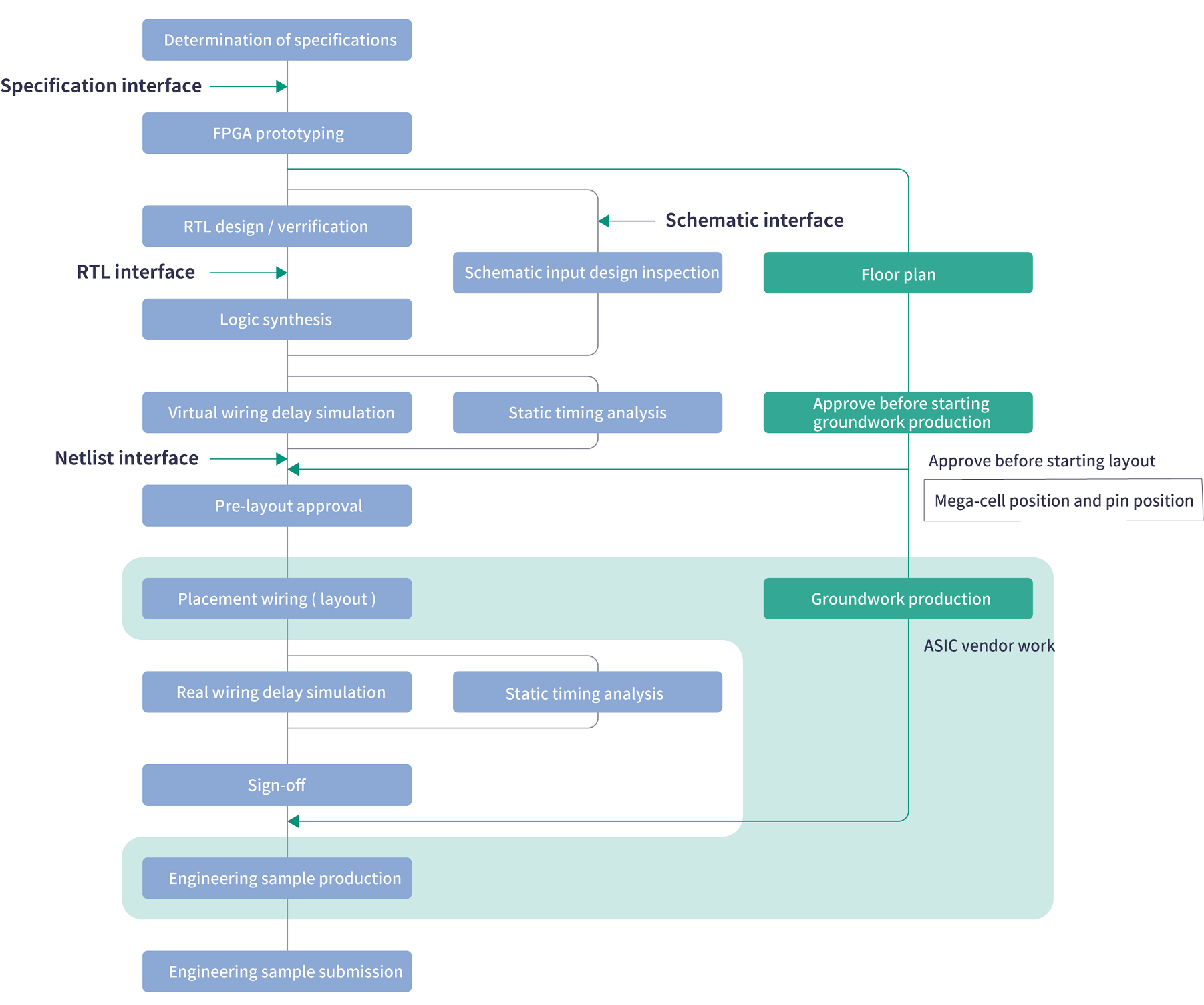

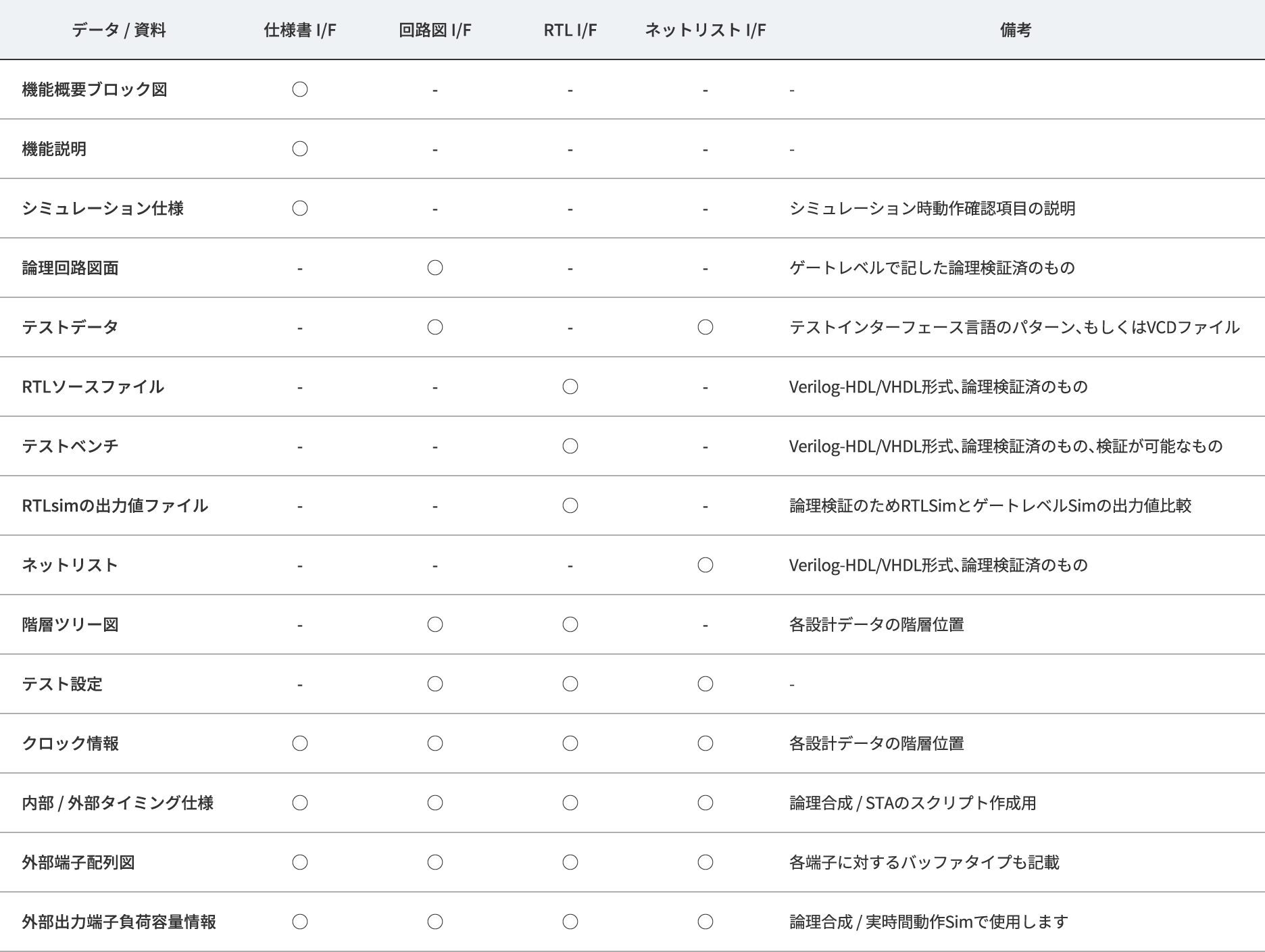

Semiconductor / Electronic devices

Semiconductor / Electronic devices -

FA System / Control equipment

FA System / Control equipment -

Power electronics / Renewable energy

Power electronics / Renewable energy -

Semiconductor manufacturing equipment / Measuring instruments

Semiconductor manufacturing equipment / Measuring instruments -

Pneumatic hydraulic equipment / conduction equipment

Pneumatic hydraulic equipment / conduction equipment -

Electronic materials / Chemical materials

Electronic materials / Chemical materials -

Defense products / Telecommunications Infrastructure

Defense products / Telecommunications Infrastructure -

Broadcasting-related

Broadcasting-related -

ICT / DX / EC

ICT / DX / EC

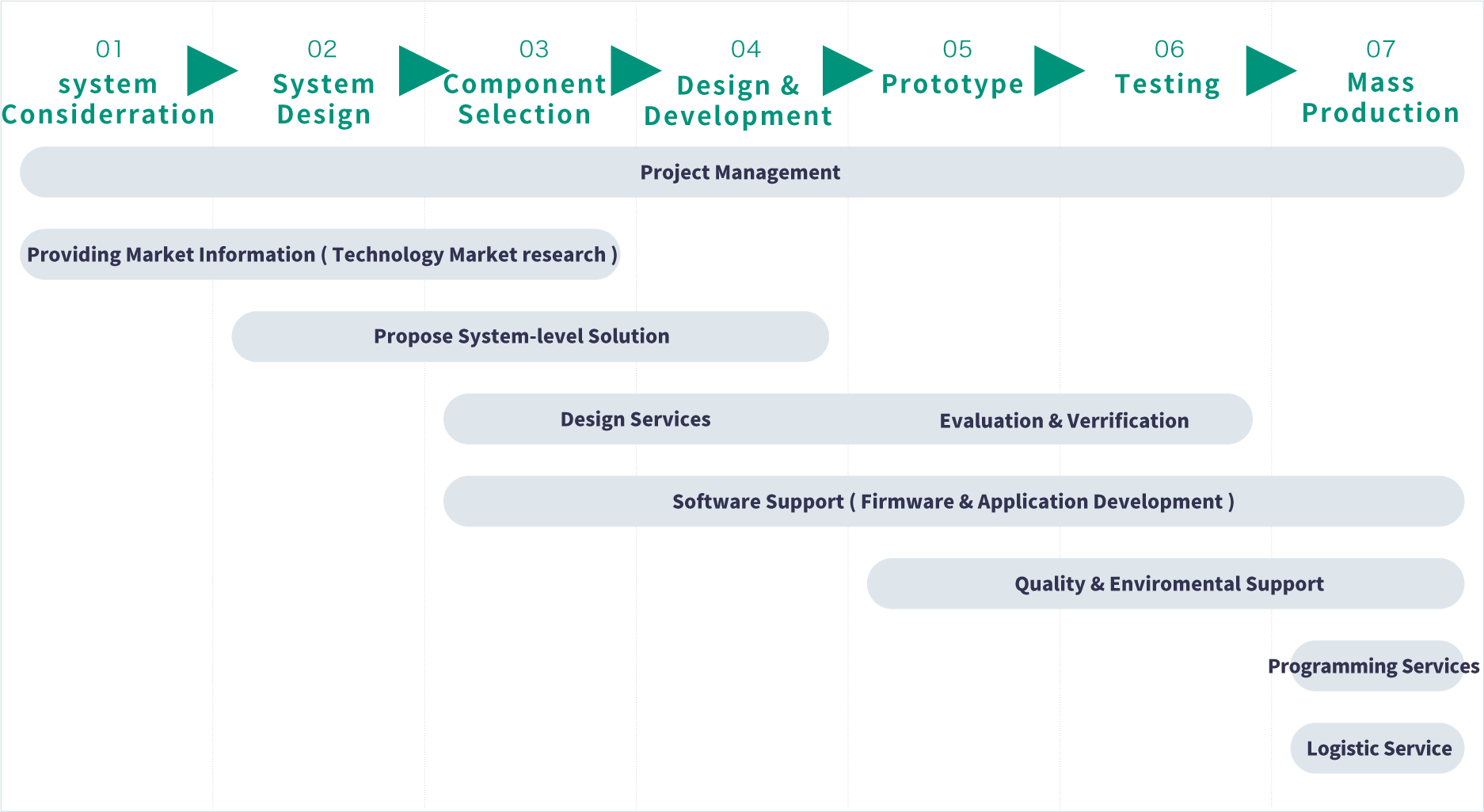

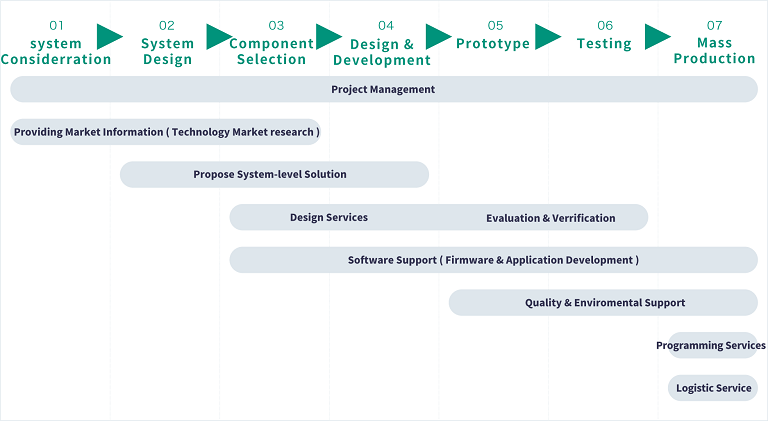

Technical ServiceService

View More

NetworkNetwork

View More