Service技術サービス

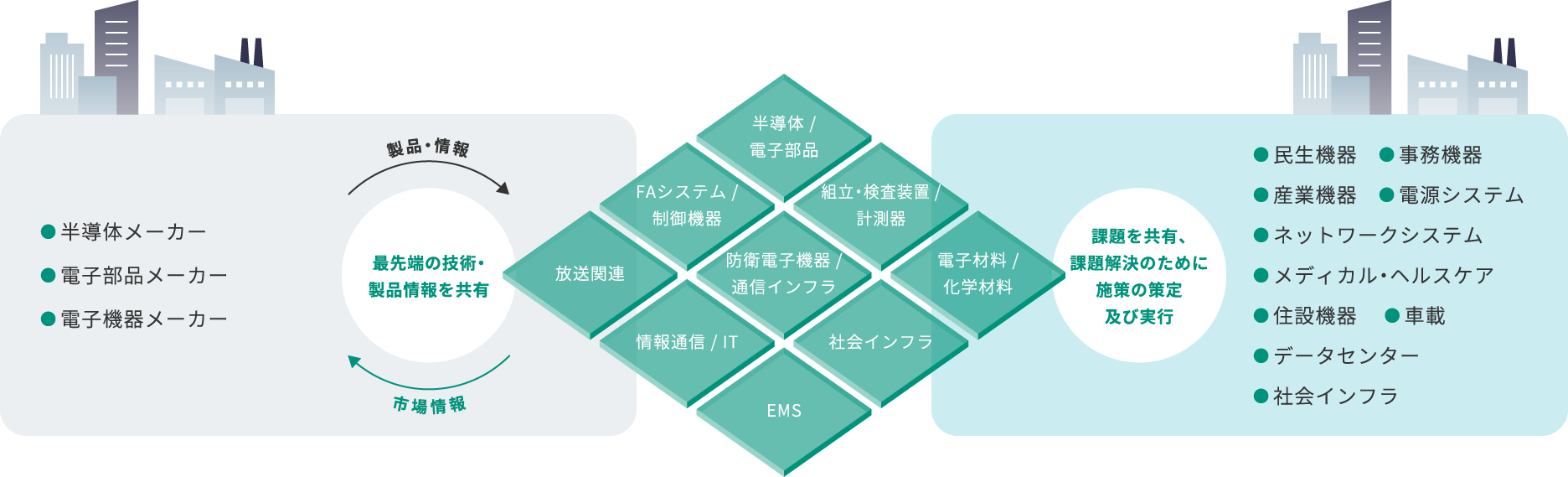

各分野に精通したFAEと営業担当者が、最善のソリューションを提案します。

当社では、製品化に向けて仕様検討の段階からFAEが参画。半導体メーカーとの密接なリレーションとともに、ハードウェア・ソフトウェア両面からのソリューション提案及び徹底したデザイン活動を行います。

プロジェクトマネージメントはもとより、評価・検証、品質・環境サポート等を組み合わせたFAEサポートをご提供いたします。

技術情報やネットワーク、豊富な開発実績を活かして、仕様書からのASIC受託設計開発、お客様とメーカーとのASIC開発インターフェースサポート、FPGA及び評価基板の受託設計など、さまざまなご要望にお応えします。

| 仕様書 I/F | 仕様書渡し開発 |

|---|---|

| 回路図 I/F | 図面渡し開発 (回路図 + テストベクタ) |

| RTL I/F | RTL渡し開発(RTL記述(検証済み) + テストベンチ) |

| FPGA I/F | FPGAデータ渡し開発(RTL or 回路図 + テストベクタ or テストベンチ) |

| ネットリスト I/F | 仕様書渡し開発(ネットリスト + テスターパターン or VCDファイル) |

回路図入力 : Work Veiw(PC版)

Simulator : NC-Verilog,Verilog-XL、ModelSim SE

Debugger : Verdi

Sign Off Tool : VSO(東芝Verilog Sign Off)

論理合成ツール : Design Compiler(論理合成ツール)

解析ツール : Prime Time(静的タイミング解析ツール)

FPGA : ALTERA、XILINX

| データ / 資料 | 仕様書 I/F | 回路図 I/F | RTL I/F | ネットリスト I/F | 備考 |

|---|---|---|---|---|---|

| 機能概要ブロック図 | ◯ | – | – | – | – |

| 機能説明 | ◯ | – | – | – | – |

| シミュレーション仕様 | ◯ | – | – | – | シミュレーション時動作確認項目の説明 |

| 論理回路図面 | – | ◯ | – | – | ゲートレベルで記した論理検証済のもの |

| テストデータ | – | ◯ | – | ◯ | テストインターフェース言語のパターン、もしくはVCDファイル |

| RTLソースファイル | – | – | ◯ | – | Verilog-HDL/VHDL形式、論理検証済のもの |

| テストベンチ | – | – | ◯ | – | Verilog-HDL/VHDL形式、論理検証済のもの、検証が可能なもの |

| RTLsimの出力値ファイル | – | – | ◯ | – | 論理検証のためRTLSimとゲートレベルSimの出力値比較 |

| ネットリスト | – | – | – | ◯ | Verilog-HDL/VHDL形式、論理検証済のもの |

| 階層ツリー図 | – | ◯ | ◯ | – | 各設計データの階層位置 |

| テスト設定 | – | ◯ | ◯ | ◯ | – |

| クロック情報 | ◯ | ◯ | ◯ | ◯ | 各設計データの階層位置 |

| 内部 / 外部タイミング仕様 | ◯ | ◯ | ◯ | ◯ | 論理合成 / STAのスクリプト作成用 |

| 外部端子配列図 | ◯ | ◯ | ◯ | ◯ | 各端子に対するバッファタイプも記載 |

| 外部出力端子負荷容量情報 | ◯ | ◯ | ◯ | ◯ | 論理合成 / 実時間動作Simで使用します |

以下の2種類のテストデータ/テストベンチが必要になります。

お問い合わせやご相談は、

専用フォームよりお願いいたします。